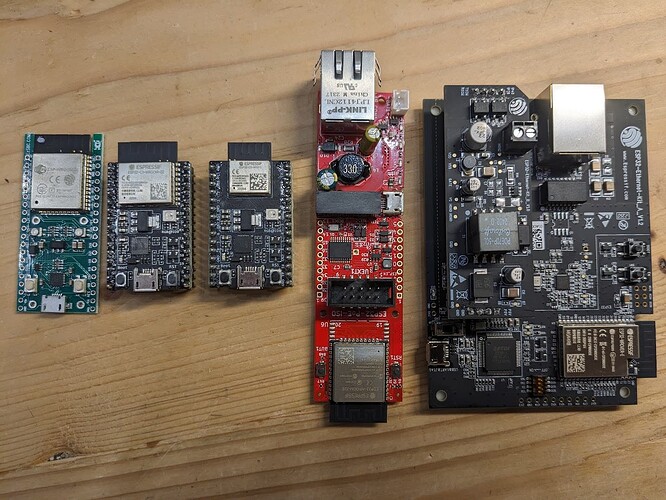

This topic is to explore running Zephyr on ESP32 devices. To start, we have four boards:

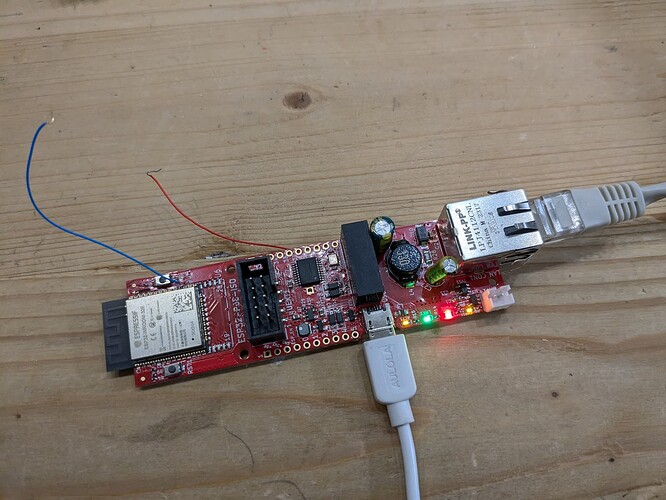

- Olimex ESP32-POE-ISO (ESP32-WROOM-32E module, Xtensa)

- EzSBC ESP32 Breakout and dev board (ESP32-WROOM-32 module, Xtensa)

- ESP32-C-DevKitC (ESP32-C3-WROOM-02, RiscV)

- ESP32-C-DevKitM (ESP32-C3-MINI-1, RiscV)

Two boards with the ESP32-WROOM modules (Xtensa microprocessor) and two boards with the ESP32-C3 (RISC-V).

The process to build and flash Zephyr is similar for both architectures:

C3 RiscV:

west build -b esp32c3_devkitm --sysbuild samples/hello_world

Xtensa:

west build -b esp_wrover_kit --sysbuild samples/hello_world

And to flash:

west flash

You can run tio on the serial port to view the console.

ESP-ROM:esp32c3-api1-20210207

Build:Feb 7 2021

rst:0x1 (POWERON),boot:0xc (SPI_FAST_FLASH_BOOT)

SPIWP:0xee

mode:DIO, clock div:2

load:0x3fcc1e00,len:0x1fd0

load:0x403b6e00,len:0x7844

load:0x403bee00,len:0x1200

entry 0x403b92e6

I (48) boot: MCUboot 2nd stage bootloader

I (48) boot: compile time May 23 2024 18:07:00

I (48) boot: Multicore bootloader

I (49) spi_flash: detected chip: generic

I (52) spi_flash: flash io: dio

W (54) spi_flash: Detected size(4096k) larger than the size in the binary image header(2048k). Using the size in the binary image header.

I (67) boot: chip revision: v0.3

I (69) boot.esp32c3: SPI Speed : 40MHz

I (73) boot.esp32c3: SPI Mode : SLOW READ

I (78) boot.esp32c3: SPI Flash Size : 4MB

I (81) boot: Enabling RNG early entropy source...

I (97) spi_flash: flash io: dio

[esp32c3] [INF] Image index: 0, Swap type: none

[esp32c3] [INF] Loading image 0 - slot 0 from flash, area id: 1

[esp32c3] [INF] Application start=40380730h

[esp32c3] [INF] DRAM segment: paddr=000136f0h, vaddr=3fc836c0h, size=0053ch ( 1340) load

[esp32c3] [INF] IRAM segment: paddr=00010040h, vaddr=40380000h, size=036b0h ( 14000) load

[esp32c3] [INF] DROM segment: paddr=00020000h, vaddr=3c000000h, size=005B0h ( 1456) map

[esp32c3] [INF] IROM segment: paddr=00030000h, vaddr=42010000h, size=02508h ( 9480) map

*** Booting Zephyr OS build v3.6.0-4560-g11920e35a00e ***

Hello World! esp32c3_devkitm/esp32c3

The development process feels very similar between the Xtensa and RiscV devices.

Next steps will be to configure the WiFi networking and the Ethernet on the Olimex board.